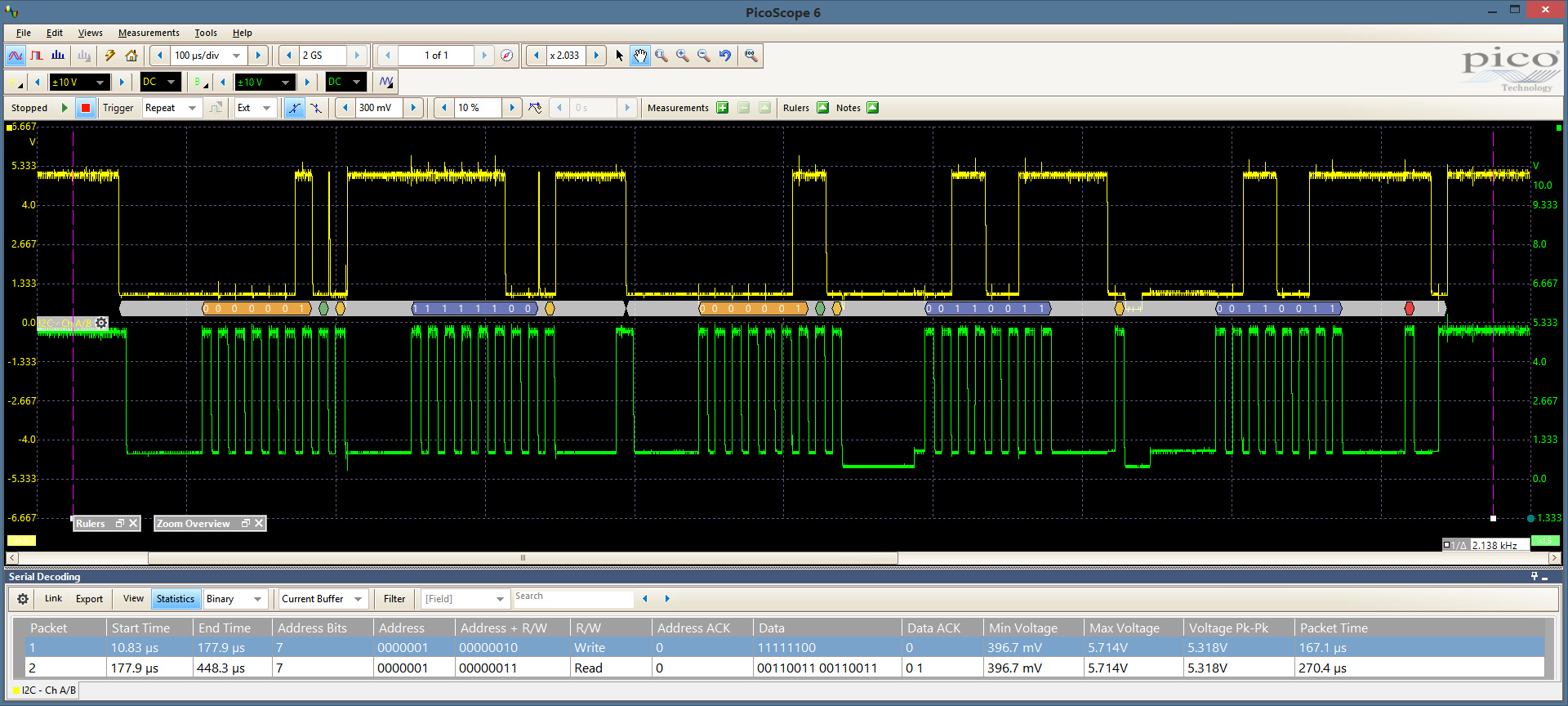

This is an update to a post that I made a week or so ago. I’ve reverted to using hardware and had good results this week. It took a lot of trial and error, but here we go:

When the master implementation is finished, I plan to make the source public. It needs some hardening though, it’s not terribly robust when it comes to bus failures, but we’ll be tightened up by Friday. In the meantime, anyone know why clock and data are floating at about 1v when driven low? This is all Microchip hardware controlled and there are only two devices on the bus being pulled up by 2K2 resistors…

Just as a follow-up, 2k2 was not enough resistance. With 4k7 and subsequently less current on the bus lines when drained, lines are easily pulled low by one device.